2年

关键词 |

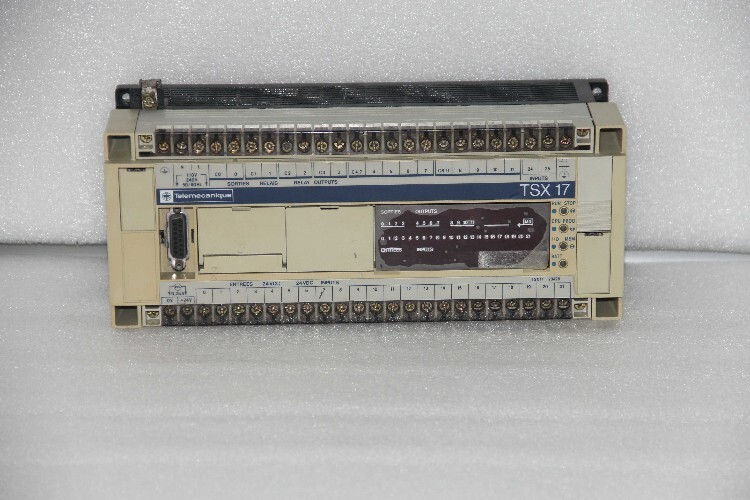

浙江施耐德模块,施耐德模块生产厂家,施耐德模块厂家,施耐德模块厂家 |

面向地区 |

全国 |

140DDI35300 内置多层缓存 CPU 从不直接访问 RAM。现代 CPU 有一层或多层缓存。CPU 执行计算的能力比 RAM 向 CPU 提供数据的能力要快得多。其原因超出了本文的范围,但我将在下一篇文章中进一步探讨。 高速缓存比系统 RAM 更快,并且更接近 CPU,因为它位于处理器芯片上。高速缓存提供数据存储和指令,以防止 CPU 等待从 RAM 中检索数据。当 CPU 需要数据时——程序指令也被认为是数据——缓存会判断数据是否已经驻留并将其提供给 CPU。 如果请求的数据不在缓存中,它会从 RAM 中检索并使用预测算法将更多数据从 RAM 移动到缓存中。缓存控制器分析请求的数据并尝试预测需要从 RAM 中获取哪些额外数据。它将预期的数据加载到缓存中。通过将一些数据保存在比 RAM 更快的高速缓存中更靠近 CPU,CPU 可以保持忙碌状态,而不会浪费等待数据的周期。 我们的简单 CPU 具有三级缓存。第 2 级和第 3 级旨在预测接下来需要哪些数据和程序指令,将数据从 RAM 中移出,并将其移至更靠近 CPU 的位置,以便在需要时准备就绪。这些缓存大小通常在 1 MB 到 32 MB 之间,具体取决于处理器的速度和预期用途。

140CPU43412 CPU时钟和控制单元 140CPU43412包括所有 CPU 组件都同步才能顺利协同工作。控制单元以由时钟速度确定的速率执行此功能,并负责通过使用遍及整个 CPU 的定时信号来指导其他单元的操作。 随机存取存储器 (RAM) 尽管 RAM 或主存储器在此图和下图中显示,但它并不是 CPU 的真正组成部分。它的功能是存储程序和数据,以便在 CPU 需要它们时可以使用它们。

为了让程序员设计出一个完整的程序,需要编写三个组件。 TSXCUSBMBP中央处理器代码: 通常用C 编程语言编写,CPU 代码通过调用由 Maxeler 编译器公开的适当函数来控制执行并使用 DFE 作为处理单元。 内核集: 每个内核都实现了一定的功能,大致相当于一个函数抽象。它有一组输入流和一组附加的输出流。

管理器是将数据流从 CPU 连接到接收内核的组件,反之亦然。它在内核和 LMem 之间建立连接并互连内核。管理器还构建了 CPU 代码与 DFE 交互的接口。 管理器和内核是用一种称为 MaxJ 的特定领域语言编写的。这种语言是Java 编程语言的超集,具有一些更适合更轻松地创建数据流程序的扩展。 编译器将内核的描述转换为数据流图,该图由后端物理布局在 FPGA 芯片上。后端通常计算量很大,因为需要考虑许多结构约束。

TRICONEX MA2211-100 I/O 模块是一种可扩展的模块化解决方案,可集成到 Premio 的工业计算机中,并通过即插即用的可扩展性提供增强的可靠性。这些附加模块有助于解决在崎岖边缘出现的设计限制和兼容性问题。TRICONEX MA2211-100 I/O 模块提供定制以满足特定 I/O 要求,从而在严苛的边缘部署中实现稳健的 I/O 连接。 采用专有的 PCIe 通信标准设计构建,它创建了一个简单的,但多功能的解决方案可以在兼容的 Premio 系统之间互换,以实现完全优化的配置。EDGEBoost 模块直接安装到各自的 EDGEBoost 支架中,为用户提供了一种可扩展的方式来扩展他们的 I/O 需求,而无需进一步投资来为更多物联网设备提供动力。

TRICONEX 的 MA2211-100 I/O 主要特性 通过 PCIe 协议的互操作性 MA2211-100 I/O 通过 Premio 的专有引脚设计进行设计,可轻松集成到兼容的 Premio 系统中,并且可以互换以获得更优化的配置。通过标准化的PCIe 协议,EDGEboost I/O 模块直接插入兼容 Premio 产品中的 EDGEboost 支架,允许中央系统与其连接的设备之间进行无缝通信。EDGEBoost I/O 模块能够支持新的变革性技术,例如 M.2 NVMe 存储和 M.2 AI 加速器,以实现实时推理功能。

全国施耐德模块热销信息