来源:深圳长欣自动化设备有限公司 时间:2024-05-20 10:44:07 [举报]

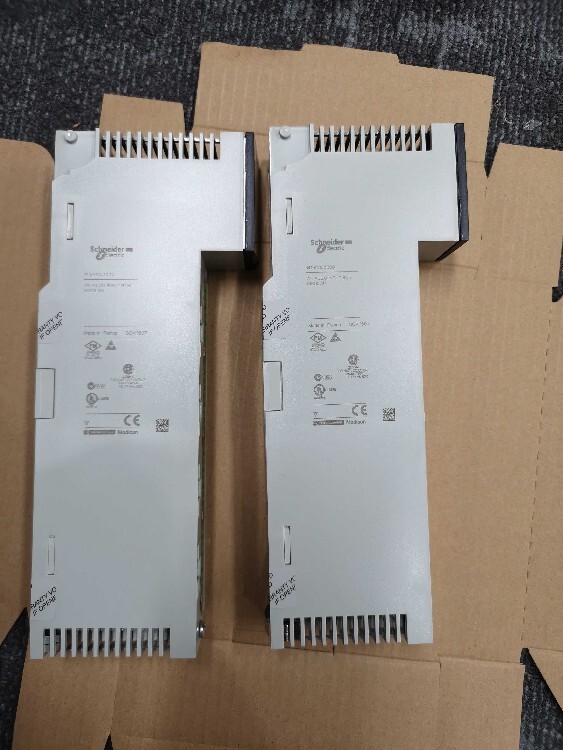

140DDI35300 内置多层缓存

CPU 从不直接访问 RAM。现代 CPU 有一层或多层缓存。CPU 执行计算的能力比 RAM 向 CPU 提供数据的能力要快得多。其原因超出了本文的范围,但我将在下一篇文章中进一步探讨。

高速缓存比系统 RAM 更快,并且更接近 CPU,因为它位于处理器芯片上。高速缓存提供数据存储和指令,以防止 CPU 等待从 RAM 中检索数据。当 CPU 需要数据时——程序指令也被认为是数据——缓存会判断数据是否已经驻留并将其提供给 CPU。

如果请求的数据不在缓存中,它会从 RAM 中检索并使用预测算法将更多数据从 RAM 移动到缓存中。缓存控制器分析请求的数据并尝试预测需要从 RAM 中获取哪些额外数据。它将预期的数据加载到缓存中。通过将一些数据保存在比 RAM 更快的高速缓存中更靠近 CPU,CPU 可以保持忙碌状态,而不会浪费等待数据的周期。

我们的简单 CPU 具有三级缓存。第 2 级和第 3 级旨在预测接下来需要哪些数据和程序指令,将数据从 RAM 中移出,并将其移至更靠近 CPU 的位置,以便在需要时准备就绪。这些缓存大小通常在 1 MB 到 32 MB 之间,具体取决于处理器的速度和预期用途。

假设计算机已收到从内存位置 10 读取数据的指令。为执行读取操作,140CPU65260该CPU 将 R/W 线提升到高电平以激活内存电路,为读取操作做准备。几乎同时,位置 10 的地址被放置在 AB 上。16位二进制(0000 0000 0000 1010)中的数字10被发送到AB中的内存中。10对应的二进制电信号操作内存中的特定电路,使该位置的二进制数据被放置到DB中。CPU 有一个内部寄存器,在读取操作期间被激活以接收和存储数据。然后CPU根据相关指令在下一个运行周期中处理数据。

每当 CPU 将数据从其内部寄存器之一发送到内存时,就会执行类似的操作,这是一种“写”操作。在这种情况下,R/W 线将设置为与读取操作相反的逻辑电平(即本例中的低电平)。写操作时,将要发送的数据放在DB中,同时目的地址放在AB中。此操作会将数据从 CPU 源位置传输到目标位置,目标位置可以是RAM中的内存位置,也可以是外部设备

SCHNEIDER 140CRA31200 PCI设备

CPU和所有 PCI 设备都需要访问它们共享的内存。140CRA31200设备驱动程序控制 PCI 设备并通过使用此内存在它们之间传递信息。通常,此共享内存包含设备的控制和状态寄存器,用于控制设备和读取其状态。例如,PCI 140CRA31200 设备驱动程序会读取其状态寄存器以找出设备是否准备好写入信息块,或者它可能写入控制寄存器以在设备打开后启动设备。

CPU 的系统内存可用于此共享内存,但在这种情况下,每次 PCI 设备访问内存时,CPU 都暂停,等待它完成。对内存的访问通常一次于一个系统组件。这会减慢系统速度。它不允许系统的外围设备以不受控制的方式访问主内存。这将是非常危险的;发生故障的设备可能会使系统非常不稳定。

外围设备有自己的内存空间。CPU 可以访问这些空间,但是通过使用 DMA(直接内存访问)通道,设备对系统内存的访问受到非常严格的控制。ISA 设备可以访问两个地址空间;ISA I/O(输入/输出)和 ISA 内存。对于的微处理器,PCI 具有三个要素:PCI I/O、PCI 内存和 PCI 配置空间。

一些微处理器,例如 Alpha AXP 处理器,除了系统地址空间之外,不能自然访问地址空间。该处理器使用支持芯片组访问其他地址空间,例如 PCI 配置空间,通过使用稀疏地址映射方案窃取部分大型虚拟地址空间并将其映射到 PCI 地址空间。

为了让程序员设计出一个完整的程序,需要编写三个组件。

TSXCUSBMBP中央处理器代码:

通常用C 编程语言编写,CPU 代码通过调用由 Maxeler 编译器公开的适当函数来控制执行并使用 DFE 作为处理单元。

内核集:

每个内核都实现了一定的功能,大致相当于一个函数抽象。它有一组输入流和一组附加的输出流。

管理器是将数据流从 CPU 连接到接收内核的组件,反之亦然。它在内核和 LMem 之间建立连接并互连内核。管理器还构建了 CPU 代码与 DFE 交互的接口。

管理器和内核是用一种称为 MaxJ 的特定领域语言编写的。这种语言是Java 编程语言的超集,具有一些更适合更轻松地创建数据流程序的扩展。

编译器将内核的描述转换为数据流图,该图由后端物理布局在 FPGA 芯片上。后端通常计算量很大,因为需要考虑许多结构约束。

地址解码器控制对特定设计的内存和 I/O 寄存器的访问。通常,可编程逻辑器件 (PLD) 用于将每个存储芯片分配给特定范围的地址。特定范围内的输入地址代码会生成片选输出,从而启用该设备。I/O 端口寄存器,设置为处理进出系统的数据传输,也通过相同的机制分配特定地址,并由 CPU 以与内存位置相同的方式访问。分配给特定外围设备的地址称为内存映射。

IS200DSVOH1A是GE公司开发的伺服端子板。它是 GE Mark VI 涡轮机控制卡。几十年来,Mark VI 系统一直用于控制工业蒸汽和/或燃气轮机系统。

该板的目的是作为特定执行器或传感器的直接接口。典型的 Mark VI 系统中将使用多张卡。该组件是一个盒子中带有两个输入/输出通道的端子板。它有两个伺服电流源和六个 lvdt/lvdr 反馈传感器。

脉冲率输入范围为 2 至 14k Hz。PCB是一块又长又窄的矩形板。它的两个角有安装孔。在电路板的上部中心边缘附近,两个端子排并排放置。两个垂直母连接器位于下边缘。板上还有两个二位母插头。

其他电路板组件包括继电器、十几个跨接开关、晶体管、集成电路、电容器和电阻器。该板带有板 ID 号、代码 6BAO1 以及各种组件标识符。

IS200STCIH1A 是GE Mark VI 下的DIN RAIL 接触式输入卡。该系统是 GE 终推出的 Speedtronic 蒸汽或燃气轮机管理系统之一。Speedtronic 系列从 20 世纪 60 年代的 Mark I 开始,一直到 1990 年代的 Mark VI 和 Mark VIe,包含众多系统。

Mark VI 通常由具有外部短路保护的 125 V 直流电池系统供电。该系统可由 120/240 伏电源供电,并使用电源转换器整流为 125 伏直流电。

IS200STCIH1A是一块微型板,元件选择有限。

单个母 37 针(D 型)连接器位于板的长边之一的中心。

具有 51 个连接的两层端子排沿着电路板的另一个长边延伸。这被称为TB1。三位母插头位于电路板上端子排的后面。

IS200STCIH1A 中只有一个集成电路。(U1.) 它有大约 80 个电阻、几条二极管线和各种电容器。

每个角都有一个小钻孔,端子排末端有两个端子孔 (E1/E2),PCB 表面有两个较大的孔。

这些可以在每个短边上找到。代码 3212、类型 6 和 FA/00 均印在组件上。板号可以在板表面的两个位置找到。

标签:吉林施耐德模块,施耐德模块厂家,施耐德模块生产厂家,施耐德模块厂家